Half Adder VHDL (Structural style modelling)

The Half Adder circuit in Digital Electronics is used to add two 1-bit numbers and the circuit generates Sum and Carry as the outputs of this operation.

The VHDL code for Half Adder circuit is written with structural modelling by using andgate and xorgate as components.

VHDL Code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity halfadder is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Sum : out STD_LOGIC;

Carry : out STD_LOGIC);

end halfadder;

architecture structural of halfadder is

component andgate is

port(a,b: in std_logic;

y: out std_logic);

end component;

component xorgate is

port(a,b: in std_logic;

y: out std_logic);

end component;

begin

G1: andgate port map(A,B,Carry);

G2: xorgate port map(A,B,Sum);

end structural;

VHDL Code for andgate is used from previous post.

VHDL code for xorgate is written using Dataflow style modelling.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity xorgate is

Port ( a,b : in STD_LOGIC;

y : out STD_LOGIC);

end xorgate;

architecture dataflow of xorgate is

begin

y <= a xor b;

end dataflow;

Testbench:

Testbench is to be written for Half Adder and not for components, which are already tested by applying the testbench for each of them.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY haalfadder_tb IS

END haalfadder_tb;

ARCHITECTURE behavior OF haalfadder_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT halfadder

PORT(

A : IN std_logic;

B : IN std_logic;

Sum : OUT std_logic;

Carry : OUT std_logic

);

END COMPONENT;

--Inputs

signal A : std_logic := '0';

signal B : std_logic := '0';

--Outputs

signal Sum : std_logic;

signal Carry : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: halfadder PORT MAP (

A => A,

B => B,

Sum => Sum,

Carry => Carry

);

-- Stimulus process

stim_proc: process

begin

A<='0'; B<='0';

wait for 10 ns;

A<='0'; B<='1';

wait for 10 ns;

A<='1'; B<='0';

wait for 10 ns;

A<='1'; B<='1';

wait for 10 ns;

end process;

END;

USE ieee.std_logic_1164.ALL;

ENTITY haalfadder_tb IS

END haalfadder_tb;

ARCHITECTURE behavior OF haalfadder_tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT halfadder

PORT(

A : IN std_logic;

B : IN std_logic;

Sum : OUT std_logic;

Carry : OUT std_logic

);

END COMPONENT;

--Inputs

signal A : std_logic := '0';

signal B : std_logic := '0';

--Outputs

signal Sum : std_logic;

signal Carry : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: halfadder PORT MAP (

A => A,

B => B,

Sum => Sum,

Carry => Carry

);

-- Stimulus process

stim_proc: process

begin

A<='0'; B<='0';

wait for 10 ns;

A<='0'; B<='1';

wait for 10 ns;

A<='1'; B<='0';

wait for 10 ns;

A<='1'; B<='1';

wait for 10 ns;

end process;

END;

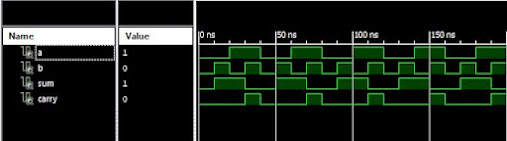

Output:

The above code is tested on Xilinx ISE Design Suite 14.7 Webpack.

It is intended only for educational purpose.

Comments

Post a Comment